Андрей Филиппов (Dec. 3,

2002)

Введение

Примерно год назад я написал статью для

онлайн издания LinuxDevices.com, и, после того

как о ней было упомянуто на Слэшдоте

моя компания (Elphel Inc.)

стала получать много запросов на универсальную сетевую камеру, а не высокоскоростную

со стробируемым усилителем яркости, о которой я писал. Камера модели 303,

обеспечивая высокое разрешение, не была способна поддерживать высокую

частоту кадров - процессору ETRAX100LX требуется около 5 секунд для JPEG

сжатия цветного изображения размером 1280 х 1024 пикселей.

Высокоскоростная камера с усилителем яркости

В предыдущей статье я упомянул о своем намерении увеличить

частоту кадров, но способ реализации оказался совсем другим, чем я

планировал. Я решил не использовать микросхему для сжатия изображений по

стандарту JPEG-2000 фирмы Analog Devices. Я также не воспользовался

гибридным модулем ETRAX multi-chip module фирмы Axis Communications,

так как мне хотелось иметь в системе больше памяти (и оперативной, и

флэш), чем они туда поместили. И наконец, в камере не нашлось места для

FPGA Quicklogic, которую я планировал использовать для компенсации

неодинаковости пикселей сенсора (fixed-pattern noise elimination) -

реализация этой функции требует раз в 10 меньше ресурсов, чем сжатие

изображений, поэтому для нее всегда найдется место в той же

FPGA.

Вместо этого я решил попробовать сделать . . .

Реконфигурируемую камеру на основе открытого

кода

Для начала я решил исследовать возможность использования

достаточно большой универсальной перепрограммируемой микросхемы FPGA для

осуществления ввода изображения, его предварительной обработки и сжатия

(например, по стандарту baseline JPEG) со скоростью, не меньшей, чем

обеспечивает сенсор (около 20 МГц пиксельная частота). Дополнительно, я

хотел, чтобы работа с FPGA поддерживалась бесплатным программным

обеспечением, чтобы пользователи смогли не только самостоятельно

скомпилировать и собрать программное обеспечение камеры из исходных

текстов, но и сделать то же самое с аппаратным (FPGA).

Я не совсем

уверен в правомерности называть FPGA аппаратной (hardware) частью, так как

для ее модификации не нужно даже открывать корпус камеры. Но есть, по

крайней мере, два аргумента, что это все-таки "железо": (1) можно сжечь

устройство при загрузке неверного кода в FPGA (на этапе начальной отладки

мне приходилось держать палец на микросхеме); и (2) - скорость -- а,

именно, стократное увеличение производительности и то, что камера сжимает

изображения примерно в 2,5 раза быстрее, чем мой компьютер (на основе

Athlon-700) может их декодировать, при том, что обе операции требуют

примерно одинакового объема вычислений. И при этом FPGA работает без

вентиллятора и лишь незначительно теплее окружающей среды.

Выбор

FPGA

Подходящую кандидатуру было найти легко - ей оказался

новейший (см. примечание внизу) член семейства недорогих FPGA фирмы Xilinx

- Spartan IIe (300 тыс. вентилей) - XC2S300E. К тому же, он поддерживается

бесплатным ПО (ISE Webpack), которое хорошо работало в моем проекте и

одбеспечило утилизацию 98% ресурсов микоросхемы.

К сожалению,

бесплатная версия симулятора, поставляемая с ISE Webpack, оказалась

практически бесполезной для моих целей, так, как установленный в ней

предел на 500 строк исходного текста, не серьезен для такого проекта. Я

надеюсь, что это не очень серьезная проблема для пользователей Линукс и

можно использовать какой-нибудь из симуляторов с открытым кодом.

Перед тем, как начинать само проектирование (а в то время у меня не

было опыта работы с устройствами и ПО Xilinx), мне нужно было убедиться,

что планируемые функции возможно реализовать на микросхеме такого размера.

Для этого я стал искать коммерческие IP и обнаружил, что они действительно

существуют (хотя и довольно дорогие), а значит, выбранная микросхема

Xilinx вполне пригодна для поставленных целей.

Я также нашел заметку по применению Xilinx (XAPP610 application note), которая содержала исходный текст реализации двумерного

дискретного косинусного преобразователя, использующего примерно 30% ресурсов

и достаточно быстро работающего (позднее я обнаружил, что он все-таки

не совсем подходит, и мне его пришлось существенно переработать).

Архитектура камеры

Я смог приступить к реализации проекта в августе, когда я установил ПО

Xilinx, разработал электрическую схему камеры и печатную плату, сделав

ее точно такого же размера, как и для предыдущей модели.

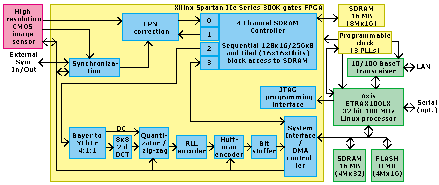

Блок-схема: Реконфигурируемая сетевая камера Elphel 313

(нажмите для открытия полноразмерного изображения)

Вместе с новой микросхемой FPGA пришлось добавить

некоторые дополнительные компоненты . . .

- 16MБ SDRAM памяти, подключенной непосредственно (и только) к FPGA,

так что обработка изображений не ограничивает пропускной способности

шины центрального процессора.

- многоканальный программируемый генератор тактовых сигналов: его 20

МГц фиксированный (от кварцевого осциллятора) выход и один PLL (25МГц)

использованы для ЦПУ и приемо-передатчика локальной сети,

соответственно, сохраняя два оставшихся программируемых канала для

тактирования FPGA. Это устройство (CY22393FC) фирмы Cypress удачно

совмещает энергонезависимую память (так что необходимые сигналы поступят

на ЦПУ и м/с локальной сети сразу при подаче питания) и

I2C-совместимый интерфейс, который в камере добавляет уровень

гибкости к реконфигурируемой м/с FPGA.

Реконфигурируемая FPGA программируется из файла (bit-stream), который

получается в результате работы ПО Xilinx и записывается во флэш память

камеры. Информация пересылается в FPGA через 4 вывода универсального порта

ЦПУ, подключенных к специализированным JTAG выводам FPGA. Единственная

строка в одном из загрузочных скриптов ("cat /etc/x313.bit >

/dev/fpgaconfjtag") и доля секунды для исполнения - все что требуется

чтобы запустить FPGA.

Программа FPGA разработана вокруг четырехканального контроллера SDRAM.

Он использыет встроенные блоки памяти ("Block RAM" - всего в XC2S300E 16

таких блоков размером 4096 бит каждый) для буферизации каждого канала по

принципу "пинг-понг" (пока одна половина наполняется, другая -

опорожняется, потом - наоборот). Контроллер обслуживает следующие 4

канала:

- Канал 0 -- по выбору: либо исходные, либо обработанные данные

от сенсора (формата 8 или 16 бит/пиксель). Данные записываются в память

блоками формата 256 х 1 пиксель (128 х 1 для 16-битного формата).

Возможна запись частичного блока (последнего в строке).

- Канал 1 -- используется для чтения из памяти калибровочной

информации, заренее подготовленной ЦПУ. Для каждого пикселя считывается

по два 8-битовых поля. Первое - значение, которое необходимо отнять от

входных 10-битовых данных, поступающих от приемника изображений

("темновая картинка"). Предумотрено дополнительное масштабирование этих

данных в 2 и 4 раза. Второе поле содержит мультипликативный коэффициент

(обратный чувствительности ячейки), который, в зависимости от режима,

позволяет индивидуально корректировать ячейки в диапазонах +/-12.5%,

+/-25% или +/-50%.

- Канал 2 -- поставляет данные в цепочку блоков JPEG кодера.

Для выбранного видеоформата 4:2:0, в котором две цветовые компоненты (Cb

и Cr) имеют в 2 раза меньшее разрешение (по обоим направлениям), чем

сигнал яркости Y (а это соответствует информации, поступающей от сенсора

с мозаичным фильтром), минимальный элемент кодирования (minimal coding

unit - MCU) составляет квадратный блок 16х16 пикселей, котроые далее

кодируются как 4 блока для яркости (8х8 пикселей каждый) и по одному 8х8

блоку для каждой из двух цветовых компонент (всего 6 на MCU). В том

случае, если сжатие осуществляется одновременно с регистрацией,

контроллер SDRAM обеспечивает сигнал готовности, который сообщает, что в

памяти содержится (записано каналом 0) по крайней мере на 16 строк

больше информации, чем уже обработанно компрессором.

- Канал 3 -- обеспечивает двухсторонний доступ ЦПУ к памяти.

При нормальной работе он служит для считывания необработанной информации

(записанный приемником изображений по каналу 0) и записи калибровочной

информации (для канала 1), которая вычисляется программным способом на

основе считанных неодработанных данных.

Контроллер работает на частоте 75 МГц (ширина шины данных - 16 бит),

что достаточно для обеспечения квази-одновременного доступа каналов при

частоте считывания около 25 МГц.

Модуль синхронизации позволяет

камере регистрировать асинхронные события. Камера позволяет работать с

сенсорами фирмы Зоран (форматов 2/3, 1/2 и 1/3 дюйма) и Кодак (1/2 дюйма),

который имеет только режим работы "rolling shutter". В этом случае

асинхронное событие (например, лазерный импульс) будет, вероятно,

зарегистрирован в двух последовательных кадрах. Так как камера постоянно

считывает информацию в кольцевой буфер (а время экспозиции каждого пикселя

в точности равно периоду кадров), возможно воссоздание полного

изображения. Модуль синхронизации работает в двух режимах (аналогичных

"внешней" и "внутренней" синхронизации осциллографа) - с использованием

электрического сигнала запуска или без него, когда постонно происходит

сравнение просуммированных значений пикселей каждой строки с заранее

установленным значением (при этом подпороговые значения зарегистрированные

до срабатывания не пропадают, так как обрабатываются приксели как после,

так и до срабатывания). Последний режим позволяет регистрировать короткие

световые импульсы без дополнительных электрических подключений к

камере.

Собственно JPEG сжатие изображений (использующее более 2/3 ресурсов)

осуществляется цепочкой связанных модулей, некоторые из которых используют

встроенные блоки памяти "Block RAM" для буферизации данных и/или хранения

таблиц (квантизационных и Хаффмана):

- Первая стадия -- преобразование данных цветного сенсора, в

котром к каждом блоке из четырех (2х2) пикселей есть 2 с зеленым

фильтром (по диагонали), один - с красным и один - с синим, в формат

YCbCr 4:2:0. На вход поступает квадратный блок из 16х16 пикселей,

преобразователь сканирует его построчно и записывает в два буфера

одновременно - 16х16 для яркостного сигнала Y и 2х8х8 - для

цветоразностных. Одновременно вычисляются средние значения для каждого

из 6 получаемых 8х8 блоков (DC компоненты), которые затем вычитаются и

поступают на квантизатор в обход DCT преобразователя. На выход данные

поступают последовательно, шестью блоками по 64 элемента, 4 для яркости

и по одному для каждого из цветоразностных. Три последующих стадии

обработки (DCT, квантизатор и RLL кодер) расчитаны на обработку данных,

где каждый блок из 64 элементов постуает непрерывно, а между блоками

допустимы любые (в том числе и нулевые) перерывы.

- Вторая стадия -- двумерный дискретный косинусный

преобразователь (8x8), основаный на

href="http://www.xilinx.com/xapp/xapp610.pdf">заметке по применению

Xilinx. Мне пришлось его несколько переработать, чтобы обеспечить

поблочно-асинхронную работу и увеличить разрядность данных,

обрабатываемых без переполнения. Этот модуль использует блок памяти

2х64х10 бит для буферизации данных ("пинг-понг") между горизонтальной и

вертикальной стадиями двумерного преобразования. Но выход данные

поступают блоками по 64 значения (с фиксированной задержкой относительно

входных) в по-столбцовом порядке (сверху вниз, затем слева

направо).

- Третья стадия -- квантизатор/зиг-заг комбинирует данные,

полученные из двух источников - 8-ми битовые (со знаком) данные среднего

значения в блоке и 12-битные (со знаком) данные от модуля DCT. Модуль

использует два блока памяти - для хранения двух альтернативных пар

квантизационных таблиц (64х12 бит каждая) и для переупорядочивания

данных в 8х8 зиг-загом (от более низких к более высоким пространственным

частотам (согласно JPEG). Такой порядок увеличивает вероятность длинных

непрерывных последовательности нулей, необходимых для эффективности

работы следующей (RLL) стадии. Квантизатор использует умножение на

12-битные данные вместь деления на 8-ми битные, при этом, для уменьшения

возможной ошибки, программа, генерирующая таблицы, корректирует их так,

что делители (записываемые в заголовоке файла) соответствуют

мультипликативным коэффициентам, загружаемым в FPGA (до начала

компрессии).

- Четвертая стадия -- кодер RLL является первым в цепочке,

который разрывает обработку однородными блоками по 64 отсчета. На выходе

он комбинирует данные, полученные от квантизатора с данными счетчика

последовательных нулей. Эта стадия также поддерживает хранение

предыдущего значения постоянной составляющей (DC) каждой из трех (Y, Cb,

Cr) компонент, т.к., согласно JPEG, кодированию подлежат разности DC

значений, а не они сами.

- Пятая стадия -- кодер Хаффмана использует на входе FIFO

размером 256x16. Еще три блока памяти использованы собственно для

хранения двух таблиц (2х256х20), где на вход поступает 8 бит, подлежащих

кодированию, а с выхода одновременно получаются 16 бит данных и 4 бита

длины данных (1-16). Таблицы кодирования DC компонент короткие, и они

размещены в неиспользованных разделах таблиц для AC. Эта стадия, как и

последующая, использует удвоенную тактовую частоту по сравнению с

предыдущими. Это позволяет успевать кодировать даже в случае отсутствия

нулей на выходе RLL (может возникнуть при очень низкой степени сжатия и

исходном изображении содержащем широкий пространственный спектр)

- Шестая стадия -- комбинирует битовые последовательности

произвольной длины в выходные слова фиксированного размера (16 бит). На

этой стадии также вставляются байты 0x00 после каждого 0xff, как это

требуется для формата файлов JFIF, где 0xff является началом маркера.

Выходные данные поступают в FIFO размером 256х16, на выходе

объединяются попарно в 32-х разрядные слова и передаются в системную

память по каналу прямого доступа ЦПУ.

Результаты и

планы

Код компилируется в 98% ресурсов FPGA, это занимает около

20 минут на компьютере на основе Athlon 700МГц. И запрограммированная FPGA

раборает - и работает по-настоящему быстро! Компрессор поддерживает полную

скорость сенсора (15 к./сек для 1280х1024). В английском оригинале статьи

я написал, что некоторые кадры выпадают - сейчас это все исправлено и

камера посылает 15 к/сек при 1280х1024 (61 к/сек для 640х480, 223 к/сек

для 320х240, 700к/сек для 160х128) через стандартую локальную

сеть.

Реконфигурируемяа сетевая камера модель 313

В камере пока нет видеосервера и она позволяет получать

видеоклипы формата Quicktime некоторой предопределенной (хотя может быть и

достаточно большой) длины. Для просмотра этих клипов одновременно с их

генерацией в начале файла должен содержаться полная информация о размере

кадров, поэтому, т.к. размер сжатого кадра заранее не известен, приходится

их в этом случае "подравнивать", добавляя нули в конце. При этом есть

возможность автоматической подстройки степени сжатия (по результатам

предыдущего кадра), чтобы поддерживать примерно одинаковый

размер.

18 ноября, 2002, Xilinx объявил о двух новых членах

семейства Spartan IIe - с 600 тыс. вентилей и 400 тыс. Большего размера

микросхема использует большего размера корпус, а та, которая имеет размер

400 тыс вентилей может быть установлена в камеру без всяких переделок

печатной платы. Я думаю, что в этом случае удастся реализовать MPEG

кодировщик для полного кадра.

Ниже приводится описание камеры,

которая получилась в результате...

О реконфигурируемой сетевой камере Elphel

313

Cуществует много сетевых камер (т.е. камер, которые

позволяют передавать изображения в локальную сеть или интернет без

дополнительного компьютера) различных производителей. Некоторые из них

обеспечивают достаточно высокую частоту кадров, но размер изображений

ограничен 705x480 пикселей или меньше. Существуют также сетевые камеры

высокого (мегапиксельного) разрешения, но в них сжатие одного полного

кадра занимает от одной до нескольких секунд.

Камера модели 313 совмещает высокое разрешение с высокой частотой

кадров. Это сетевая камера, имеющая 1,3 мегапикселя, которая позволяет

передавать полные изображения с частотой 15 кадров в секунду. Высокое

разрешение камеры позволяет, например, при использовании широкоугольного

объектива, наблюдать за помещением из одного угла без использования

механических поворотно-сканирующих платформ.

Высокая частота кадров при полном размере изображений позволяет

обходиться без "цифрового поворота" ("digital pan-and-tilt"), т.е.

вырезания окна из полного кадра - обычного приема, используемого для

компенсации недостаточной скорости передачи полноформатных

изображений.

Камера получает питание (48 В пост. тока) через кабель локальной сети

по стандарту IEEE 802.3af. Использование относительно высокого

напряжения, соответствующего параметрам разъемов и кабелей (которые были

изначально разработаны для телефонных сетей), позволяет устанавливать

камеру на в 4 раза большем удалении, чем при питании 24 В, и в 16 раз -

чем при 12 В - напряжениях, которые до сих пор используются в некоторых

сетевых камерах (вопреки стандарту IEEE 802.3af).

Все встраиваемое программное обеспечение камеры (и прошивка FPGA)

записаны во флэш памяти и могут быть обновлены через интернет. В отличие

от, например, довольно опасной процедуры переписи флэш памяти с BIOS в

компьютере (при загрузке неверного файла или, если питание было

отключено во время процедуры, компьютер больше не будет запускаться)

камера использует очень удобное свойство процессора ETRAX100LX (фирмы

Axis Communications) - он имеет встроенный начальный загрузчик из

локальной сети, который не использует данные во флэш памяти. Это

означает, что процедуру загрузки нового программного обеспечиния можно

всегда начать сначала.

Камера имеет также дополнительные полезные качества для

разработчиков. Как встраиваемое ПО, так и прошивка FPGA имеют исходные

тексты, открытые для загрузки на веб-сайте (open source). Камера имеет

четыре уровня возможной модификации:

- Изменение интерфейса пользователя с помощью стандартных средств

создания веб-сайтов -- В камере есть 3 файловых системы (с

запретом записи, в RAM-диске и в jffs во флэш-памяти), что позволяет

легко экспериментировать с загружаемыми страницами с возможностью

вернуться к исходному состоянию, если что-нибудь не

получилось.

- Приложения, написанные на языке С -- Их можно

скомпилировать и собрать на компьютере, работающем под ОС Линукс,

используя исходные тексты на странице загрузок (и ссылок, которые там

есть). Полученные исполняемые файлы могут быть пересланы на камеру с

помощью ftp и сохранены на RAM или во флэш память (jffs). Создаваемые

приложения могут иметь интерфейс CGI и отвечать на соответствующие

http запросы веб-браузеров.

- Добавление (или модификация) драйверов ядра операционной

системы -- Для этого необходимо скомпилировать и собрать новое

ядро ОС, после этого есть возможность как загрузки камеры с новым

ядром через сеть (при этом запись во флэш память не производится и при

перезапуске камера вернется в исходное состояние), или запись нового

ядра во флэш память, тогда новое ПО будет запускаться при включении

камеры.

- Измение прошивки FPGA дает возможность в полной мере

воспользоваться мощностью реконфигурируемых распределенных

вычислительных возможностей камеры -- Для этого необходимы другие

инструменты - программное обеспечение для разработки FPGA фирмы Xilinx

(есть версия для свободной загрузки через интернет) и исходные тексты

FPGA камеры, которые есть на веб сайте Elphel.

![]() src="/sites/default/files/articles/andrey_filippov.jpg" vspace=5

src="/sites/default/files/articles/andrey_filippov.jpg" vspace=5

width=85>Об авторе: Андрей Николаевич Филиппов

страстно увлечен применением современных технологий для встраиваемых компьютерных

устройств, особенно в области ввода и обработки изображений. У него более

двадцати лет опыта исследований и разработок в области высокоскоростных

аналогово-цифровых систем, программируемых микросхем, микропроцессорных

устройств и их программного обеспечения, для целей, в том числе, ввода и

обработки изображений в лазерной физике и автоматизации научных исследований.

У Андрея Николаевича ученая степень кандидата физ.-мат. наук (Ph.D.), полученная

в Московском физико-техническом институте. Фото автора сделано высокоскоростной

камерой с усилителем яркости.

|