10393

10393 is the system board of Elphel NC393 series camera. It will also replace 10353 board in [[Elphel_Eyesis4Pi|Eyesis4pi] and other Elphel multi-sensor cameras. It has the same physical dimensions as 10353 and may be used as an upgrade to the previous camera modules.

This camera system board is designed to simultaneously support multiple sensors - both with legacy parallel interface (it is directly compatible with 10338 Sensor board and 10359 Sensor multiplexer board) and with new high-speed serial interface (up to 8 lanes + clock per each port). Sensor ports of the 10393 can be combined to interface larger/higher speed sensors, interface supply voltage is programmable in the range of 1.35V to 2.8V. All the sensor port interface signals are routed directly to the FPGA pads (22 I/O signals on each of the 4 flex cable connectors) , so the same ports can be uses for other purposes, for example to control the motors or interface IMU of the quadcopter.

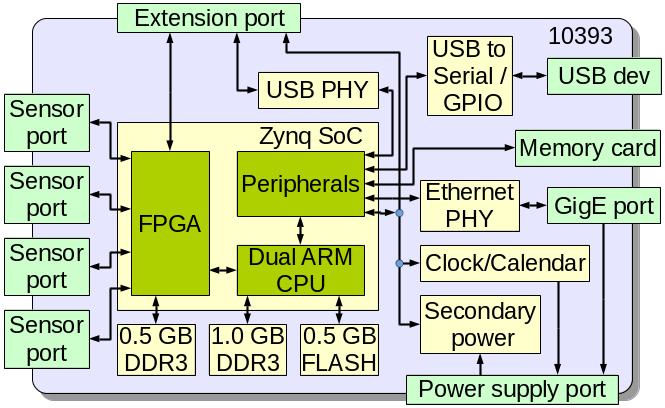

Block diagram below shows major parts and I/O ports of the 10393 board. Left edge of the diagram corresponds to the sensor connections, right one - to the camera back panel with external connectors, top and bottom contain inter-board connections:

- The system is built around Xilinx Zync SoC that combines a dual-core ARM processor, a rich set of the standard peripherals and FPGA on the same chip. This combination provides high bandwidth connection between the processors and the FPGA fabric.

- 4 identical sensor ports are 30-conductor 0.5mm pitch flex cable connectors, compatible with the earlier Elphel products. These connectors are split into two pairs, so they are closest to one short edge of the board - two on each side. Combined with an external multiplexer boards (at the expense of proportionally lower frame rate) each 10393 can work with up to 16 sensors (12 with the existing 10359 board).

- 500MB of the dedicated DDR3 memory is connected directly to the FPGA portion of the SoC, with the 16-channel image-optimized controller it provides efficient access to the memory for simultaneous image acquisition, compression and image processing. We plan to implement such functionality as real-time image de-warping and correlation of images from multiple sensors for the 3d data extraction.

- 1GB of DDR3 memory (2 chips providing 32-bit data bus) is uses as a system RAM for the Processor subsystem.

- 500MB of NAND flash provide program storage.

- Persistent program storage is expandable with the micro-SD cards (not easy to see on the photo as the slot is hidden under the network connector). This interface provides bootable memory, so it is always possible to restore the camera functionality even if the system NAND will be accidentally flashed with corrupted image.